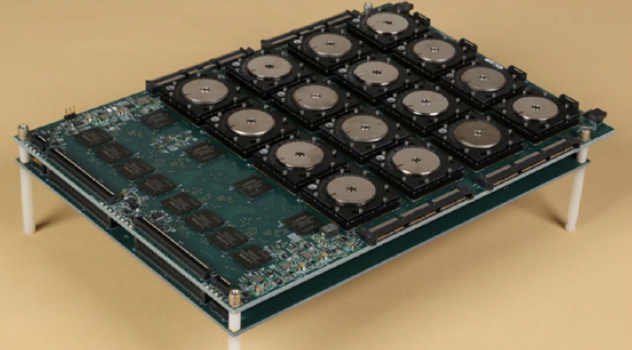

Neuromorphic Chip : Present and Future

- 뉴로모픽칩은 학습기반의 인공지능에 최적화된 하드웨어로 제4차산업혁명을 가속화할 잠재성이 높음

- 특히 뉴로모픽칩을 활용하는 SW기술이 수반돼야 할 필요성 존재

- A neuromorphic chip, optimized hardware for learning mechanism of artificial intelligence, has high potential to accelerate the forth industrial revolution

- SW technology will be needed to fully utilize neuromophic chip